## Second Generation IEEE 802.3at PSE Multi-Port Test Suite

for the PowerSync<sup>®</sup>Analyzer & Programmable Load

## **Product Overview**

# **Key Features**

- □ In-Depth System Testing of IEEE 802.3at PSE's

- □ Concurrently Analyze Up To 192 PSE Ports

- □ Fully Automated Testing and Reporting

- □ Assess PSE Power Administration Decisions

- □ Assess PSE Power Management Behaviors

- □ Robust Emulation of Type-1 and/or Type-2 PD's

- □ PoE LLDP Emulation of Type-1 and/or Type-2 PD's

- □ Easily Configured, Single Sequence Testing of All PSE's

- □ Static and Transient Reserve Capacity Analysis

- □ Formulate PD Powering Uncertainty Metrics

- □ Formulate PSE Port Uniformity Metrics

- □ Assess PSE Power Reliability Over Time

## IEEE 802.3at PSE's

End-Span PSE's Type 1 & 2, LLDP, 2-Event Mid-Span PSE's Type 1 & 2 PoE/PoE+ Powered Jacks

## Fully Automated System Testing

Up to 192 PSE Ports Easily Configured & Sequenced Colorful, Informative Reporting with Graphics

## Assess Critical System Parameters

Class-Based Processing Static Power Capacity Transient Reserve Multi-Port LLDP Granting Power Uncertainty Power Uniformity

## Multi-Platform Support

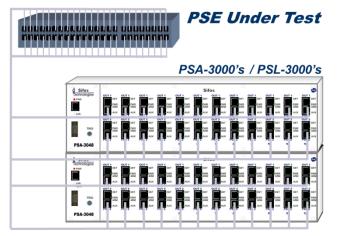

PSA-3000 / PSA-3048 PSL-3000 / PSL-3024

#### Overview

The **PSE Multi-Port Test Suite** is a component of the **PSE Multi-Port Suite** for PowerSync<sup>®</sup> Analyzers and Programmable Loads. This fully automated group of tests and reporting takes the PowerSync Analyzer (PSA) and its proven PSE Conformance Testing Capabilities into the realm of fully automated PSE System Power Management and Multi-Port Behavior testing.

Whereas PSE Conformance Testing assesses compliance of each standalone PSE port to 802.3at specifications, Multi-Port Testing assesses system-wide behaviors only observable when many PD's are powered by a PSE. The PSE Multi-Port Test Suite will acquire and distill information regarding key behaviors of a PSE including class-based power administration, multi-port LLDP granting, power-up and LLDP grant timing, static power capacity, transient reserve capacity, power down timing, power-per-port uniformity and uncertainty, and power stress test analyses.

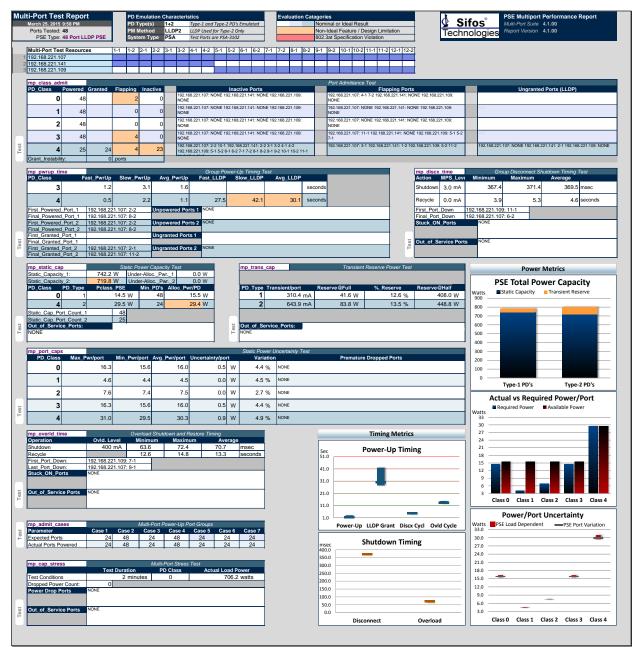

The second generation Multi-Port Test Suite is easily configured to cover all required PD emulations such that system testing of Type-2 and Type-1 PSE's is performed in a just a **single sequence**, with up to 38 limitchecked parameters produced on a **single, graphic-rich Microsoft Excel report.**

The standard report\* generated by the Multi-Port Test Suite organizes all parameters by Multi-Port Test and by PD emulation (e.g. Class 4, Type-1, etc.) with colorful annotations for parameters that represent non-ideal or design-constrained behaviors and, for certain parameters, IEEE 802.3at specification violations.

The **PSE Multi-Port Suite** is available as a feature option to all Sifos PSA-3000 and PSL-3000 chassis-based platforms. The Multi-Port Suite also includes **Live PD Emulation** for use with interactive testing of PSE administrative and power management behaviors. Live PD Emulation is described separately in Sifos datasheet **Multi-Port Live PD Emulation Overview**.

#### **PSE Multi-Port Tests**

Class-Based Powering & Granting Multi-Port Power-Up & LLDP Timing Multi-Port Disconnect Timing Static Power Capacity Analysis Transient Reserve Capacity Analysis Port Capacity Uniformity & Uncertainty Multi-Port Overload Response Timing Port & Class Subset Administration Power Stress Testing

#### Multi-Port System Test Automation

Automated Analysis and Reporting up to 192 PSE Ports at a Time Run Individual Tests from PSA Interactive or PowerShell PSA Sequence Selected Tests from PSA Interactive or PowerShell PSA Automated Microsoft Excel\* Report Generation with Colorful Graphics and Test-Specific Help Information

#### PSE Multi-Port Test Suite Features

- Up to 38 Limit-Checked PSE System Parameters from 9 Automated Tests

- Up to 10 802.3at PSE Conformance Parameters Produced from Multi-Port Test Cases

- Simple User Configuration Just Specify PD Emulation (Type 1, 2, or both 1 & 2) and PSE Power Granting Mode (PHY or LLDP)

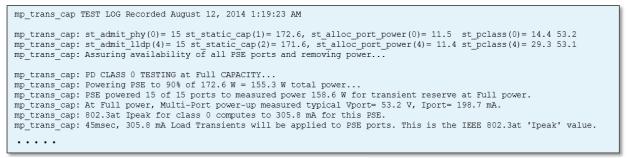

- Comprehensive Diagnostic Logging from Every Test Provides Insight to System Anomalies

- Most (8 of 9) Tests Run with Low Cost PSL-3000 Programmable Load Platform

- Increased Parameter Coverage and Granularity Available from PSA-3000 PowerSync Analyzer Platform

- \* The standard report requires Microsoft Office 2007 or newer

#### **Multi-Port Tests and Parameters**

The following tables introduce each Multi-Port test, describing the basic purpose of each test and the parameters that are measured by each test. Parameters that are accompanied by *Class N* are collected and reported per PD Class, that is, Class 0 -Class 4. Parameters that are accompanied by *Type X* are collected and reported per PD Type, that is, Type-1 and/or Type-2. Any limitations imposed on each test by the PSL-3000 Programmable Load are also described.

#### **Multi-Port Administrative Decisions and Timing Analysis**

| mp_class_admit                | Power Administ                                       | tration                                     | by PD Class and/or LLDP Request                                                                                                                                                                                                                                                                                       |

|-------------------------------|------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Objective                | (maximum) LLDP-base                                  | ed power r                                  | wer granting strategy as it relates to each PD classification and to equests. Look for instability and inconsistencies accompanying applicable, multi-port LLDP negotiations.                                                                                                                                         |

| Sequence Objective            | Provides other Multi-P classification and how        | ort tests w<br>many PSE                     | ith expectations regarding how many PSE ports will power to each PD<br>E ports will grant maximum power requests via LLDP.                                                                                                                                                                                            |

| Test Parameters<br>(Retained) | Powered Count                                        | Class N                                     | Count of ports that remain powered after multi-port power-up by PD Class. Retained values: $st_admit_phy(N)$                                                                                                                                                                                                          |

|                               | Granted Count                                        | Class N                                     | Count of ports that receive LLDP power grants for requested power level by PD Class. If Class 4 multi-port LLDP granting behavior is not repeatable (see Grant Stability below), this figure will be determined by sequencing single-port LLDP power-ups with 25.5W power requests. Retained values: st_admit_lldp(N) |

| Test Parameters<br>(Local)    | Flap Count                                           | Class N                                     | Count of ports that intermittently shut down during the multi-port power-up process by PD Class.                                                                                                                                                                                                                      |

|                               | Inactive Count                                       | Class N                                     | Count of ports that remain unpowered after multi-port power-up by PD Class.                                                                                                                                                                                                                                           |

|                               | Inactive Ports                                       | Class N                                     | List of PSA chassis' and test ports that remain unpowered by PD Class.                                                                                                                                                                                                                                                |

|                               | Flapping Ports                                       | Class N                                     | List of PSA chassis' and test ports that intermittently shut down during multi-port power-up by PD Class.                                                                                                                                                                                                             |

|                               | Ungranted Ports                                      | Class N                                     | List of PSA chassis' and test ports that do not receive LLDP power grants by PD Class.                                                                                                                                                                                                                                |

|                               | Grant Instability                                    |                                             | orts that provide 25.5W LLDP power grants given PD Class 4 across 4 cycles of<br>Ideally, this range should be zero if multi-port powering with LLDP behavior is                                                                                                                                                      |

| PSL-3000 Limitations          | NONE                                                 |                                             |                                                                                                                                                                                                                                                                                                                       |

| mp_pwrup_time                 | Multi-Port Pow                                       | er-Up a                                     | nd LLDP Grant Timing                                                                                                                                                                                                                                                                                                  |

| Test Objective                | Gain insight into the e power and LLDP pow           | efficiency o<br>er allocatio<br>or LLDP all | f PSE power management when processing multiple demands for<br>ons. Expose scenarios where PD's may be unacceptably delayed in<br>locations. Assess any vulnerability in per-port PoE service to PD                                                                                                                   |

| Sequence Objective            | This test is not prereq                              | uisite to ot                                | her Multi-Port tests.                                                                                                                                                                                                                                                                                                 |

| Test Parameters<br>(Local)    | Fast Power-Up,<br>Slow Power-Up,<br>Average Power-Up | Туре Х                                      | Time in seconds between emulated PD connection and application of power to emulated PD. Reported as minimum (or Fast) time, maximum (or Slow) time, and average time across all ports.                                                                                                                                |

|                               | First Port Powered                                   | Туре Х                                      | Chassis address and test port that first received power.                                                                                                                                                                                                                                                              |

|                               | Final Port<br>Powered                                | Туре Х                                      | Chassis address and test port that was the last to receive power.                                                                                                                                                                                                                                                     |

|                               | Fast LLDP,<br>Slow LLDP,<br>Average LLDP             | Туре Х                                      | Time in seconds between emulated PD connection and granting of a power request to a emulated PD. Reported as minimum (or Fast) time, maximum (or Slow) time, and average time across all ports.                                                                                                                       |

|                               | First Port Granted                                   | Туре Х                                      | Chassis address and test port that first received LLDP power grant.                                                                                                                                                                                                                                                   |

|                               | Final Port Granted                                   | Туре Х                                      | Chassis address and test port that was the last to receive LLDP power grant.                                                                                                                                                                                                                                          |

|                               | Unpowered Ports                                      | Туре Х                                      | List of PSA chassis addresses and test ports that failed to apply power.                                                                                                                                                                                                                                              |

|                               | Ungranted Ports                                      | Туре Х                                      | List of PSA chassis addresses and test ports that failed to receive LLDP power grant.                                                                                                                                                                                                                                 |

| PSL-3000 Limitations          | NONE                                                 |                                             |                                                                                                                                                                                                                                                                                                                       |

| mp_discx_time               | Multi-Port Disc                                                                                                                                                                                                                                                                                                               | onnect                                                                                             | Shutdown Timing                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Test Objective              | Determine that PSE ports are uniformly responding to valid PD disconnect signatures and then autonomously (independently) managing disconnect shutdown timing. Separately, determine if a group-disconnect shutdown event is in any way detrimental to subsequent per-port PoE service under control of PSE power management. |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Sequence Objective          | This test is not prereq                                                                                                                                                                                                                                                                                                       | s test is not prerequisite to other Multi-Port tests.                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                             | Minimum, Maximum,<br>Average Shutdown T                                                                                                                                                                                                                                                                                       |                                                                                                    | Time in milliseconds between emulated PD disconnect and power removal by PSE port. Reported as minimum time, maximum time, and average time across all ports.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                             | First Port Down                                                                                                                                                                                                                                                                                                               |                                                                                                    | Chassis address and test port that first removed power. (PSA-3000 only)                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                             | Last Port Down                                                                                                                                                                                                                                                                                                                |                                                                                                    | Chassis address and test port that was the last to remove power. (PSA-3000 only)                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                             | Minimum, Maximum,<br>Average Power<br>Re-Cycle Time                                                                                                                                                                                                                                                                           |                                                                                                    | Time in seconds between emulated PD disconnect followed by a shutdown and immediate PD re-connect until power is restored by the PSE port.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                             | Stuck On Ports                                                                                                                                                                                                                                                                                                                |                                                                                                    | Ports that fail to remove power given PD disconnects.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                             | Out-of-Service Ports                                                                                                                                                                                                                                                                                                          |                                                                                                    | Ports that initially powered for the disconnect shutdown timing measurements but then fail to recycle power.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| PSL-3000 Limitations        | interval measurement<br>assessed with low res<br>disconnects and then<br>Minimum Range is '50<br>range is reported as the                                                                                                                                                                                                     | s, and cro<br>solution rai<br>again afte<br>00msec'.<br>he Maximi                                  | mmable Load) does not support programmable load transients, time<br>ss-chassis triggering, shutdown and power recycle timing is<br>nges. Shutdown states are sampled after 500msec following all port<br>er 3 seconds. If any ports have removed power at 500msec, then<br>If all ports remove power at 500msec or at 3 seconds, than that<br>um Range. Recycle power states are assessed at 15 seconds, 35<br>nds following the group disconnect shutdown. |  |  |  |  |  |  |  |

| mp_admit_cases              | Power Administ                                                                                                                                                                                                                                                                                                                | tration                                                                                            | by PSE Port Subsets                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Test Objective              | regardless of location<br>and LLDP power gran<br>location on the PSE.<br>CASE 1: PD Class 1 conn<br>CASE 2: PD Class 0 on u<br>CASE 3: PD Class 2 on e<br>CASE 4: PD Class 3 on a                                                                                                                                             | , equally a<br>nts. Ideally<br>nected to ever<br>ppermost <b>st</b><br>very EVEN p<br>middle set c | est is to determine if PSE power management treats all PSE ports,<br>ind independently when making (class based) power-up decisions<br>y, all ports should be treated independently regardless of physical<br>ery ODD port (1st, 3rd, 5th, 7th) in the Resource Configuration<br>_admit_***(0) ports in the Resource Configuration<br>port (2nd, 4th, 6th) in the Resource Configuration<br>of st_admit_***(3) ports in the Resource Configuration          |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                                                                                                                                                                               |                                                                                                    | _admit_***(4) ports in the Resource Configuration                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                             |                                                                                                                                                                                                                                                                                                                               | •                                                                                                  | ort (1st, 3rd, 5th, 7th…) in the Resource Configuration<br>port (2nd, 4th, 6th…) in the Resource Configuration                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Sequence Objective          | This test is not prerequisite to other Multi-Port tests.                                                                                                                                                                                                                                                                      |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Test Parameters<br>(Local)  |                                                                                                                                                                                                                                                                                                                               | Case M                                                                                             | Count of ports that are expected to power up (and, if applicable, provide LLDP grant) given the class-specific power-up (and, if applicable, LLDP grant) counts.                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| (2000)                      | Actual Ports<br>Powered                                                                                                                                                                                                                                                                                                       | Case M                                                                                             | Count of ports that actually powered up (and, if applicable, provided LLDP grant).                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| <b>PSL-3000</b> Limitations | NONE                                                                                                                                                                                                                                                                                                                          |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                             | O                                                                                                                                                                                                                                                                                                                             |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

### Multi-Port Power Capacity Analysis

| mp_static_cap                 | Power Administration by PD Class and/or LLDP Request                                                                                                                       |         |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Test Objective                | Measure static (or steady-state) total power available and determine if PSE is correctly and efficiently allocating all available steady-state power to powered PSE ports. |         |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Sequence Objective            | Provide other Multi-Po<br>Type-2 PD's along wit                                                                                                                            |         | th values for maximum steady state power available to Type-1 and/or the minimum steady                                                                                                                                                                                 |  |  |  |  |  |  |

| Test Parameters<br>(Retained) | /                                                                                                                                                                          | Туре-Х  | Peak total steady state output power measured given Type-X (1 or 2) PD emulation measured across all test ports. Peak power point may appear prior to or after one or more individual PSE ports start to overload and are shut down. Retained values: st_static_cap(X) |  |  |  |  |  |  |

|                               | Pclass_PSE                                                                                                                                                                 | Class N | Given the PSE port voltage at full PSE power capacity, this is the individual steady-<br>state power capacity required on each port in order to meet IEEE 802.3at steady-<br>state power capacity requirements. Retained values: st_pclass(N)                          |  |  |  |  |  |  |

| Test Parameters<br>(Retained) | Alloc_Power/PD            | Class N | Given the number of powered ports, this is essentially the total static power capacity spread to each of those ports. In the case of LLDP power grants, this figure is the total static power available to just those ports that were granted their requested power level (e.g. 25.5 watts). Retained values: st_alloc_port_power(N)         |

|-------------------------------|---------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Parameters<br>(Local)    | Min_PD's                  | Туре-Х  | This is the number of PD's that could receive maximum allowed power given PD classification, PSE static power capacity, and PSE port voltage. For Class 0, that power would be 13 watts at the PD interface, or Pclass(0) at the PSE interface, and for Class 4, that power is 25.5W at the PD interface, or Pclass(4) at the PSE interface. |

|                               | Static_Cap_Port_<br>Count | Туре-Х  | This is the count of powered ports when the peak static power capacity,<br>Static_Capacity_(Type-X), is measured. This may be the same or less than the<br>number of ports originally powered with Type-X emulation.                                                                                                                         |

|                               | Under-<br>AllocPwr1       |         | ver available for powering additional Type-1 PD's based on PSE capacity, Pclass<br>nd also considering any differences in capacity between Type-2 powering and<br>vering.                                                                                                                                                                    |

|                               | Under-<br>AllocPwr2       |         | ver available for powering additional Type-2 PD's based on PSE capacity,<br>e-2), and also considering any differences in capacity between Type-1 powering<br>? powering.                                                                                                                                                                    |

|                               | Out-of-Service<br>Ports   |         | t of chassis addresses and test ports that refuse to power up to PD Class 1<br>ollowing completion of the static power capacity measurements.                                                                                                                                                                                                |

| <b>PSL-3000</b> Limitations   | NONE                      |         |                                                                                                                                                                                                                                                                                                                                              |

mp\_trans\_cap **Multi-Port Transient Reserve Power** Test Objective Determine if PSE is keeping power in reserve to meet IEEE 802.3at allowed PD transient loads (e.g. Ipeak). If PSE allocates all available power to static (steady state) loads, there is the risk that one or more allowable PD load transients will cause one or more PSE ports to remove power, including ports that do not experience the load transient. Sequence Objective This test is not prerequisite to other Multi-Port tests. Test Parameters Transient/port The transient load current that is applied for 45 msec given Type-1 emulation and Type X either 45 msec or 9.5 msec given Type-2 emulation. It will not be lower than IEEE (Local) 802.3at Ipeak(PD Class= N) and will not be higher than Ilim min (PD Type 1 or 2). It is computed from st\_pclass(N) and st\_alloc\_port\_power(N). Reserve@Full Type X The total power reserve in watts available to support load transients for Type-1 and/or Type-2 PD emulation given a PSE operating at its maximum static power capacity. It is plotted in the PSE Total Power Capacity bar graph as gold-colored region above the dark blue static power capacity for Type-1 and Type-2 PD emulation. While it is measured starting at 90% total static power capacity, it is computed by removing the remaining 10% from the measured transient load power in order to assess just the transient reserve ABOVE 100% static load capacity. This is the percentage of power ABOVE static power capacity requirement (Pclass(N)) % Reserve Type X available to support short load transients of at least Ipeak(N) on all powered (and granted, if using LLDP) ports. Both Pclass(N) and Ipeak(N) are computed using the PSE output voltage measured at full power capacity. This parameter may range negative on PSE's that have no reserve because they cannot furnish required static power capacity, Pclass(N). Reserve@Half Total power reserve in watts available to support load transients for Type-1 and/or Type X Type-2 PD emulation given a PSE operating at one half of its maximum static power capacity. **Out-of-Service** This is a list of chassis addresses and test ports that refuse to power up to PD Class Type X Ports 1 emulation prior to assessment of Transient Reserve power. The test requires that all but one of the expected ports (=st\_admit\_\*\*\*\*(N)) MUST power up and if using LLDP, grant the power request. PSL-3000 Limitations Because this test requires programmable Load Transients, it is only available to PSA-3000 test ports and is not available to PSL-3000's.

| mp_port_caps                  | <b>PSE Port Powe</b>                      | PSE Port Power Uncertainty and Variations by PD Class                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|-------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Test Objective                | any PD powering at a PD's and on individu | From a PD's perspective, total power uncertainty is the range of possible power levels available to<br>any PD powering at a particular classification. It is dependent on PSE power allocation to other<br>PD's and on individual overload tolerance variation by PSE port. This test produces figures for total<br>power uncertainty by PD class and PSE port variation in that figure. |                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Sequence Objective            | Provide other Multi-F<br>Class.           | Port Tests v                                                                                                                                                                                                                                                                                                                                                                             | with maximum per-port static power capacity as a function of PD                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Test Parameters<br>(Retained) |                                           | Class N                                                                                                                                                                                                                                                                                                                                                                                  | The maximum static power tolerated before port shutdown on all sampled ports at each PD class. st_admit_***(N) ports are initially powered to low power and overload thresholds are scanned just one port at a time. Retained value: st_max_port_power(N) |  |  |  |  |  |  |  |

| Test Parameters<br>(Local)    | Min_Pwr/port                              | Class N                                                                                                                                                                                                                                                                                                                                                                                  | The minimum static power tolerated before port shutdown on all sampled ports at each PD class. st_admit_***(N) ports are initially powered to low power and overload thresholds are scanned just one port at a time.                                      |  |  |  |  |  |  |  |

|                               | Average_Pwr/port                          | Class N                                                                                                                                                                                                                                                                                                                                                                                  | The average power tolerated before port shutdown across all sampled ports at each PD class.                                                                                                                                                               |  |  |  |  |  |  |  |

|                               | Uncertainty/port                          | Class N                                                                                                                                                                                                                                                                                                                                                                                  | The total uncertainty range of power available to any Class N PD connecting to any port of the PSE. This is a function of power management power allocation decisions and a function of $I_{cut}$ overload threshold variation.                           |  |  |  |  |  |  |  |

|                               | Variation                                 | Class N                                                                                                                                                                                                                                                                                                                                                                                  | The percentage variation in power available to any Class N PD. This variation is purely a function of $\mathbf{I}_{\text{cut}}$ overload threshold variation across PSE ports.                                                                            |  |  |  |  |  |  |  |

|                               | Premature<br>Dropped Ports                | Class N                                                                                                                                                                                                                                                                                                                                                                                  | List of chassis addresses and test ports where individual port power capacity was heavily affected by the presence of other ports operating at minimum static power levels.                                                                               |  |  |  |  |  |  |  |

| DOL DOOD L'USING              |                                           |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

PSL-3000 Limitations NONE

| Multi-Port Load a          | nd Overload St                                                                                                                                                                                                                                                                                           | ressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| mp_overId_time             | Multi-Port Group Overload Response                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Test Objective             | Determine that PSE ports are uniformly responding to overload conditions and then autonomously (or independently) managing overload shutdown timing. Separately, determine if a group-overload event is in any way detrimental to subsequent per-port PoE service under control of PSE power management. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Sequence Objective         | This test is not prerequ                                                                                                                                                                                                                                                                                 | uisite to other Multi-Port tests.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Test Parameters<br>(Local) | Minimum,<br>Maximum, and<br>Average<br>Shutdown Time                                                                                                                                                                                                                                                     | Time in milliseconds between emulated PD overload and power removal by PSE port.<br>Reported as minimum time, maximum time, and average time across all ports. PD overload<br>applied is calculated using maximum observed individual port overload,<br>st_max_port_power(N), in mp_port_caps. PD Class emulation is one of Class 0, Class 1,<br>Class 2, or Class 3 selected to maximize both the overload level and the initially powered port<br>count.                                                                     |  |  |  |  |  |  |

|                            | First Port Down                                                                                                                                                                                                                                                                                          | Chassis address and test port that first removed power. (PSA-3000 only)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                            | Last Port Down                                                                                                                                                                                                                                                                                           | Chassis address and test port that was the last to remove power. (PSA-3000 only)                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                            | Minimum,<br>Maximum, and<br>Average Power<br>Re-Cycle Time                                                                                                                                                                                                                                               | Time in seconds between emulated PD group overload shutdown event until power is restored<br>by the PSE port. Overload magnitude and duration are determined from initial overload<br>shutdown timing measurements.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                            | Stuck On Ports                                                                                                                                                                                                                                                                                           | List of chassis addresses and test ports that fail to remove power given PD overloads.                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                            | Out-of-Service<br>Ports                                                                                                                                                                                                                                                                                  | List of chassis addresses and test ports that initially powered for the disconnect shutdown timing measurements but then fail to recycle power.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| PSL-3000 Limitations       | interval measurement<br>assessed with low res<br>disconnects and then<br>Minimum Range is '50<br>range is reported as the                                                                                                                                                                                | 00 (Programmable Load) does not support programmable load transients, time<br>s, and cross-chassis triggering, shutdown and power recycle timing is<br>solution ranges. Shutdown states are sampled after 500msec following all port<br>again after 3 seconds. If any ports have removed power at 500msec, then<br>00msec'. If all ports remove power at 500msec or at 3 seconds, than that<br>he Maximum Range. Recycle power states are assessed at 15 seconds, 35<br>at 75 seconds following the group disconnect shutdown. |  |  |  |  |  |  |

| mp_cap_stress              | Multi-Port Full         | Power Stress Test                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|----------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Test Objective             |                         | emonstrate that the PSE withstands a high static power load over a long duration of time without ausing ports to drop power either temporarily or permanently.                                                                                                                                |  |  |  |  |  |  |

| Sequence Objective         | This test is not prerec | uisite to other Multi-Port tests.                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Test Parameters<br>(Local) | Actual Load Power       | This is the actual total PSE power established while trying to attain 95% of previously measured static power capacity. The test automatically selects PD Class that enables powering to 95% of st_static_cap(N), the maximum steady state load capacity, with as many PSE ports as possible. |  |  |  |  |  |  |

|                            | Dropped Power<br>Count  | The count of events where a port removed power over the course of testing. Each shutdown on each port is deemed a power removal event.                                                                                                                                                        |  |  |  |  |  |  |

|                            | Power Drop Ports        | The list of ports that experienced one or more power drops during the course of testing. Use the log file to get further details concering how many times each port dropped power and when those drop-outs occurred.                                                                          |  |  |  |  |  |  |

|                            | Out-of-Service<br>Ports | Since the test is only powering the number of ports expected to power based on<br>st_admit_***(N), this is a list of ports that were expected to power up initially, but failed to<br>power or provide expected LLDP power grant.                                                             |  |  |  |  |  |  |

| PSL-3000 Limitations       | NONE                    |                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

#### Configuring and Running the Multi-Port Test Suite

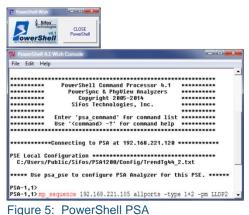

The PSE Multi-Port Suite can be accessed from either PSA Interactive Software (GUI) or PowerShell PSA, an extended Tcl/Tk command line shell.

PSA Interactive provides three top level menus: Multi-Port Live PD Emulation\*, Multi-Port PSE Tests, and Multi-

|       |       |              | Mul  | ti-Por | Resource  | Con                     | figurat                 | ion                       |                           |                           |                         |       |        |       |       |     |            |           |

|-------|-------|--------------|------|--------|-----------|-------------------------|-------------------------|---------------------------|---------------------------|---------------------------|-------------------------|-------|--------|-------|-------|-----|------------|-----------|

| Se    | lect  | PSA's        | Туре | LLDF   | Ports     |                         |                         |                           |                           |                           |                         |       |        | Tally | Ports | Tes | ted Ports: | 0         |

| PSA 1 | Ports | 192.168.1.20 | PSA  | YES    | All Ports |                         |                         |                           |                           |                           |                         |       | _      |       |       |     |            |           |

| PSA 2 | Ports | 192.168.1.21 | PSA  | YES    | 🛃 PowerS  | vnc I                   | nterac                  | tive -                    | Port S                    | elect                     | ion                     |       |        |       |       |     |            |           |

| PSA 3 | Ports |              |      |        |           | _                       |                         |                           | _                         |                           |                         | PSA P | ort Se | lecti | on    |     |            |           |

| PSA 4 | Ports |              |      |        |           |                         |                         |                           |                           |                           |                         |       | PSA SI |       |       |     |            |           |

| PSA 5 | Ports |              |      |        |           | 1                       | 2                       | 3                         | 4                         | 5                         | 6                       | 7     | 8      | 9     | 10    | 11  | 12         | ALL PORTS |

| PSA 6 | Ports |              |      |        |           |                         | -                       |                           |                           |                           |                         | _     |        |       |       |     |            |           |

| PSA 7 | Ports |              |      |        | Port 1    |                         | 1                       | ◄                         | ◄                         | ◄                         | ~                       |       | Γ      |       |       |     |            |           |

| PSA 8 | Ports |              |      |        | Port 2    | $\overline{\mathbf{v}}$ | $\overline{\mathbf{v}}$ | $\overline{ \checkmark }$ | $\overline{ \checkmark }$ | $\overline{ \checkmark }$ | $\overline{\checkmark}$ | Г     | Γ      | Γ     | Γ     | Г   |            |           |

| Clea  | f     | Load Default |      |        | Mode      |                         | Multi                   | Port                      |                           |                           |                         |       |        |       |       |     |            | SELECT    |

**Port Sequencer**. Each top level menu then provides access to the **Multi-Port Resource Configuration** menu (see Figure 1). Resource Configuration is used to define the field of instruments and test ports to be used in Multi-Port Testing. Resource Configuration automatically determines if the instrument type is a **PSA**-3000 PowerSync Analyzer or a **PSL**-3000 Programmable Load. Any mixture of PSA-3000 and PSL-3000 instruments will be treated as a **PSL**-3000 Programmable Load with corresponding test limitations.

Figure 1: Multi-Port Resource Configuration Menus

Resource Configuration also determines if **LLDP** is available to all instruments in the

Resource Configuration. If every instrument supports the LLDP emulation feature, then the test menus will enable use of Power Management modes LLDP2 and LLDP.

Once the Multi-Port Resource Configuration is defined and validated by PSA Interactive, users can run individual Multi-Port tests from the **PSE Multi-Port-2 Tests** menu (*see Figure 2*). This menu displays the Multi-Port Resource Configuration and provides several configuration options for running Multi-Port tests. These options exist within two categories:

- PD Emulation

- Power Management

PD Emulation is specified as **Type-1**, **Type-2**, or **Type-1 & 2**. **Type-1** means testing will run with PD Classes 0-3 emulated. This is the appropriate setting for Type-1 (15.4 Watt) PSE's. **Type-2** results in only PD Class 4 emulations. **Type-1 & 2** deploys PD Class 0-4

| PowerSync Interactive                                                                                                                                                                                                                                                                                                               | - Multi-Port-2 Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|